## 2025 IEEE VLSI Review

고려대학교 전기전자공학과 박사과정 이윤호

## **Session 14 Analog Techniques**

이번 2025 IEEE VLSI Session 14는 Analog 및 Mixed-Signal 회로를 주제로 총 4편의 논문이 발표되었으며, mm-Wave PLL을 위한 초고속 TDC, 저전압 동작이 가능한 SAR ADC, 대용량 load capacitor(CL)를 구동할 수 있는 3-Stage 고이득 증폭기, 그리고 고효율 배터리 구동 Class-D 오디오 앰프까지 다양한 응용 분야에서 회로 안정성과 선형성 및 전력효율을 개선하는 새로운 회로 기법들이 소개되었다. 이 가운데 본 글에서는 Gm-Boosting과 Gain-Enhancing Feedforward Path(GE-FFP)를 활용해 대용량 CL에서도 안정적으로 동작하는 3-Stage 앰프, 그리고 True-Zero-Switching(TZS) 기법을 통해 무부하 시스위칭 손실과 대기 전류를 획기적으로 줄이고 2VBAT까지 출력 전압을 부스트할 수 있는 배터리 구동 Class-D 오디오 앰프에 초점을 맞추어 살펴보고자 한다.

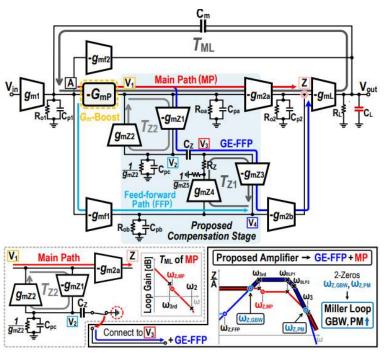

#14-3 본 논문은 대용량 커패시터를 구동해야 하는 전력 관리 및 아날로그 프런트엔드 시스템을 위해, 높은 DC 이득과 넓은 대역폭을 확보하면서 안정적으로 동작할 수 있는 3-Stage 앰프를 제안하였다. 기존 3-Stage 앰프는 큰 CL에 의해 첫 번째 극점(ω1st)이 낮아지고 Miller 루프(TML)의 중간 주파수 이득이 감소하여, 영점과 극점의 분리가 충분히 확보되지 못해 위상 여유(PM)가 줄고 불안정해지는 문제가 있다. 이를 해결하기 위해본 논문은 아래 그림 5와 같이 Gm-Boosting Cell(GmP)과 Gain-Enhancing Feedforward Path(GE-FFP)를 결합한 새로운 보상 구조를 제안하였다. 제안된 구조에서 메인 경로만 사용할 경우 기존 Active Zero 보상 앰프와 동일하게 동작하지만, GE-FFP가 추가되면 고주파에서 GE-FFP의 이득이 메인 경로보다 커져 TML의 GBW을 크게 확장시킨다. 또한 두개의 로컬 피드백 루프(TZ1, TZ2)가 상호 연관되어 Adaptive Passive Zero(A-PZ)를 형성하기 때문에, PVT 변화에도 안정적으로 위상 여유를 확보할 수 있다. 이로써 대용량 CL 구동 시에도 넓은 GBW와 충분한 PM을 동시에 달성할 수 있다.

[그림 5] 본 논문에서 제안한 Gm-boosted Amplifier의 구조

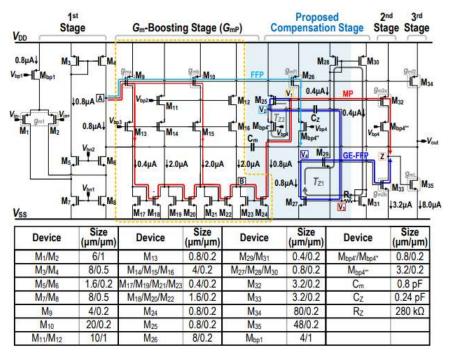

아래 그림 6과 같이 GmP는 Nested Current Mirror(NCM) 구조를 통해 38 dB의 높은 이득을 제공하면서도 고주파 극점은 GBW보다 높게 유지해 보상 복잡도를 늘리지 않는다. GE-FFP는 메인 경로(Main Path)와 병렬로 추가된 신호 경로로, 주파수가 높아질수록이득이 증가하는 특성을 이용해 TML의 GBW와 PM을 동시에 개선한다. 특히 커패시터 CZ를 접지 대신 노드 V3에 연결하여, 동일한 소자로 메인 경로의 영점(ωZ,MP)을 생성함과 동시에 GE-FFP를 형성하도록 구현하여 추가적인 소자 오버헤드를 최소화하였다. 이러한 기술들을 통해 제안된 앰프는 130 dB이상의 DC 이득과 160nF의 CL에서 1.47 MHz GBW 및 51°의 PM을 달성하며, 기존 대비 FOMS 16.9배, LC-FOMS 30.6배 향상된 성능을보여준다.

[그림 6] 본 논문에서 제안한 Gm-boosted Amplifier의 회로도

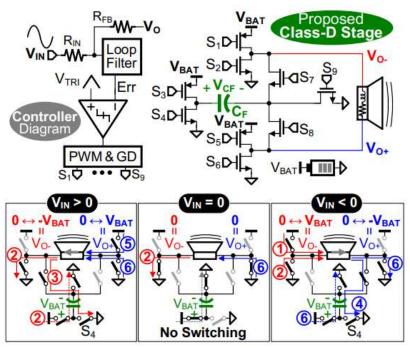

#14-4 본 논문은 배터리로 구동되는 기기에서 출력 전력(POUT)을 배터리 전압(VBAT)의 2배까지 부스트 하면서도 낮은 대기 전류(IQ)와 높은 오디오 성능을 달성하기 위해 새로운 단일단(1-stage) 부스트 Class-D 오디오 앰프를 제안하였다. 기존 Class-D 앰프는 PWM 스위칭이 입력이 0일 때도 지속되어 IQ가 커지고, 부스트 컨버터를 별도로 사용하여 2단 전력 변환에 따른 효율 저하와 추가 LC 필터가 필요하며, -VBAT 생성 방식을 적용하는 방식에선 모드 전환 시 출력에 왜곡이 발생하는 문제들이 있었다. 이를 해결하기위해 본 논문은 아래 그림 7과 같이 단일 플라잉 커패시터(CF) 기반의 부스트 토폴로지와 True-Zero-Switching(TZS) 기법을 결합한 새로운 Class-D 앰프를 제안하였다. 해당 구조는 VIN이 0보다 클 시, CF를 VBAT으로 충전한 뒤 플립하여 -VBAT을 출력에 인가하고,반대로 VIN이 0보다 작을 시, 반대 위상으로 동작시켜 fully-differential 출력(VO+&VO-)이 ±VBAT 범위를 갖도록 만든다. 이를 통해 외부 부스트 컨버터 없이도 2VBAT의 출력전압 스윙을 얻어 최대 4배의 출력 전력을 제공할 수 있다. 또한 TZS를 적용한 변조 방식은 VIN=0일 때 VO+와 VO-를 0V로 유지해 불필요한 스위칭을 억제한다.

[그림 7] 본 논문에서 제안한 Class-D Amplifier의 회로도 및 동작

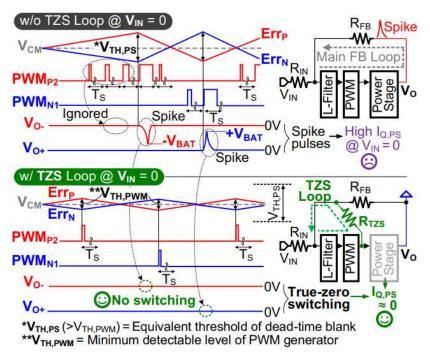

그러나 아래 그림 8과 같이 앰프 컨트롤러의 메인 루프만으로는 에러 신호(ErrP, ErrN) 가 VCM에서 서서히 드리프트해 데드타임 임계값을 넘을 시, 스위칭이 발생하고 오디오 출력에 스파이크가 생겨 불필요한 IQ 증가와 노이즈가 발생한다. 이를 방지하기 위해 제안된 TZS 보조 루프는 두 에러 신호의 차(|ErrP - ErrN|)가 PWM 검출 한계(VTH,PWM)를 초과하면 빠른 보정 펄스를 루프 필터에 공급하여 Err을 VCM으로 되돌리고, 출력 스테이지는 정적으로 접지된 상태로 유지해 스위칭 없이 IQ를 0으로 만든다. 결과적으로, 제안된 오디오 앰프는 VBAT=5V에서 ±10V 차동 출력 스윙을 제공하고, VIN=0에서 IQ를 기존 3.2mA에서 910μA로 감소시켰으며, 92.6% 피크 효율 및 3.56 W 최대 출력 전력과 -81.6 dB THD+N, 122.8 dB SNR을 달성하였다.

[그림 8] 본 논문에서 제안한 True-Zero-Switching(TZS) 루프의 동작 파형

## 저자정보

## 이윤호 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야: Power management ICs

• 이메일 : uknow@korea.ac.kr

• 홈페이지: https://sites.google.com/site/kubasiclab/home